当地时间周三,比利时微电子研究中心imec宣布,在其与ASML合作的High-NA EUV光刻实验室首次成功利用0.55NA的High-NA EUV光刻机曝光了逻辑和DRAM的图案结构。

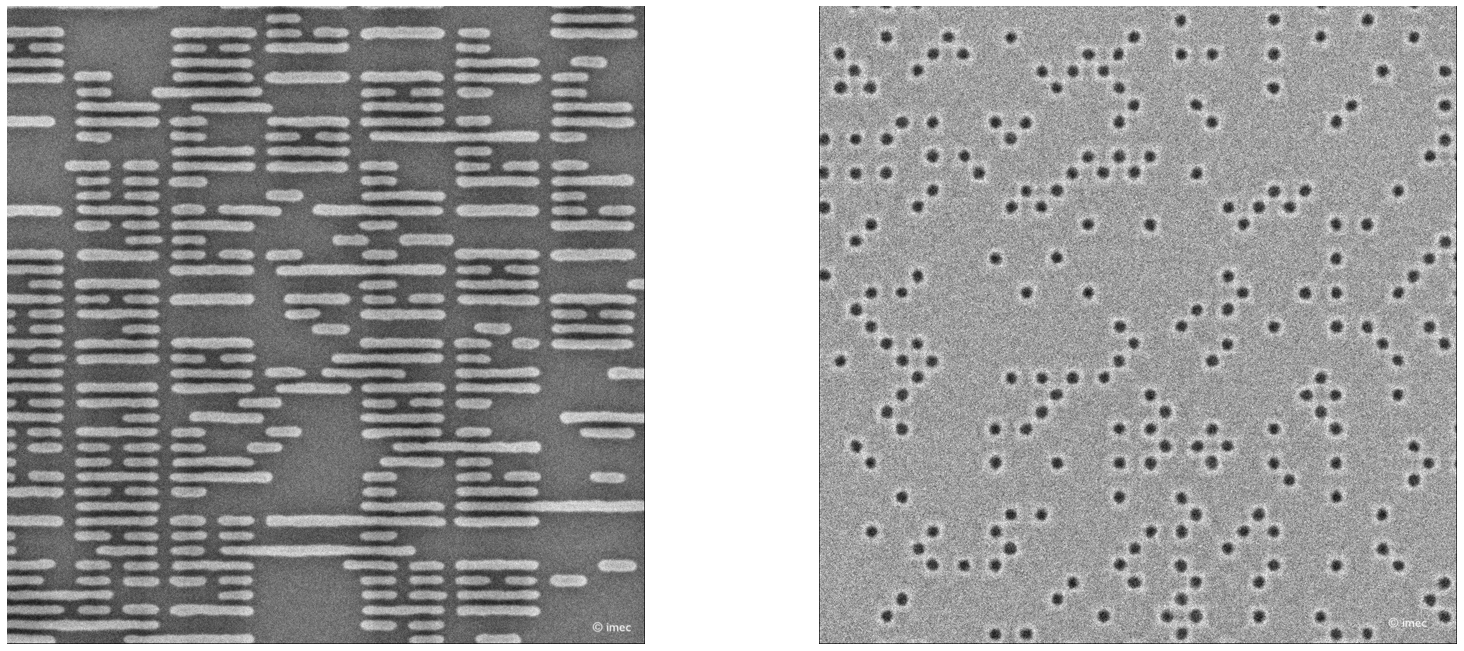

Left: 9.5nm random logic structure (19nm pitch) after pattern transfer

Right: Random vias with a 30nm center-to-center distance with excellent pattern fdelity and critical dimension uniformity

据介绍,imec 使用9.5nm密集金属线,实现了单曝光随机逻辑结构的图案化,对应于19nm pitch,将端到端间距尺寸降低至20nm以下。这足以使用单个High-NA曝光在1.4nm工艺技术上构建逻辑。

不仅如此,Imec还成功创建了中心间距为30nm的随机通孔,并具有良好的图案保真度和临界尺寸均匀性。此外,在P22nm的间距上形成的2D特征表现出了出色的性能,这足以用于3nm工艺节点的制造过程。

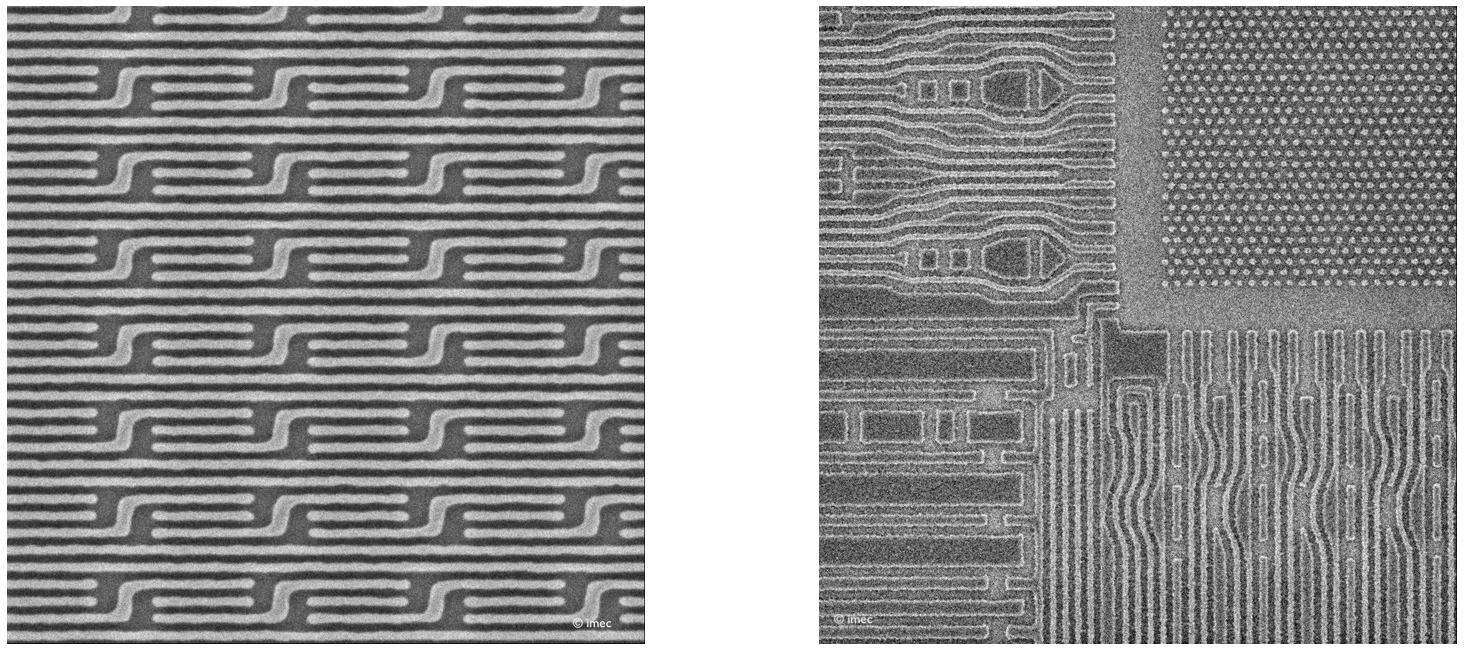

Left: 2D features at a P22nm pitch exhibited outstanding performance

Right: lmec demonstrates an integration of the storage node landing pad with the bit line periphery for DRAM

除了逻辑结构之外,imec在单次曝光中成功设计了将DRAM的存储节点着陆垫(Storage Node Landing Pad,SNLP)与位线外围集成在一起的设计,强调了High-NA技术减少曝光次数的潜力。

imec总裁兼首席执行官 Luc Van den hove 表示,作为行业应用的初步验证,结果显示了High-NA EUV技术的独特潜力,单次曝光即可实现20nm以下间距的金属层。因此High-NA EUV将对逻辑和存储器技术的尺寸扩展起到重要作用,这正是将路线图推向 "埃米时代" 的关键支柱之一。归功于ASML-imec联合实验室的建立,使我们的合作伙伴能够加快将High-NA光刻技术引入制造领域。